基于verilog的精简指令的多周期cpu处理器设计 课程论文+源码

实验报告

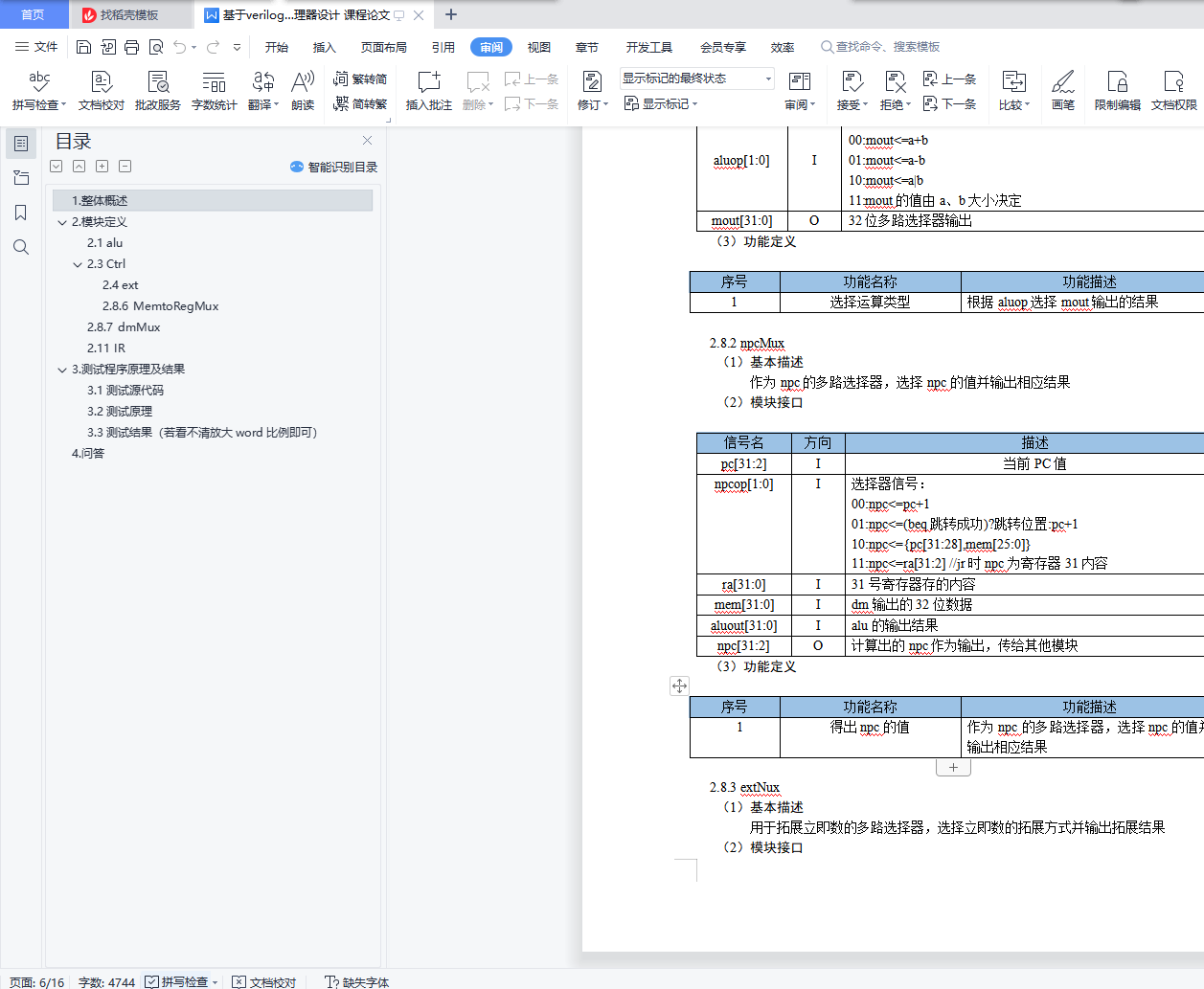

目录

1. 整体概述

该多周期处理器采用verilog开发,支持以下多条指令:{addu,subu,ori,lw,sw,beq,lui,addi,addiu,slt,j,jal,jr,lb,lh,lbu,lhu,sb,sh,slti},处理器为多周期设计。

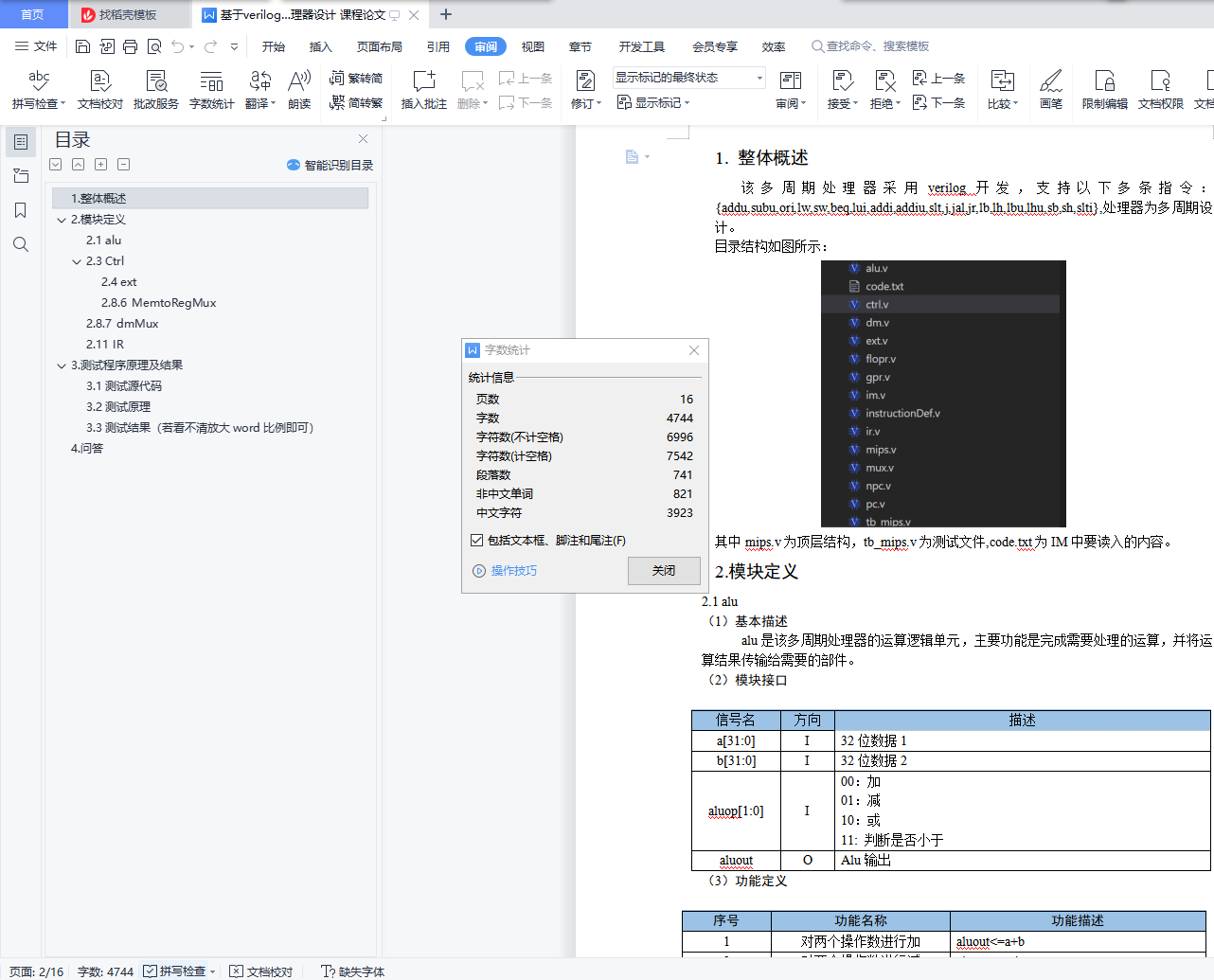

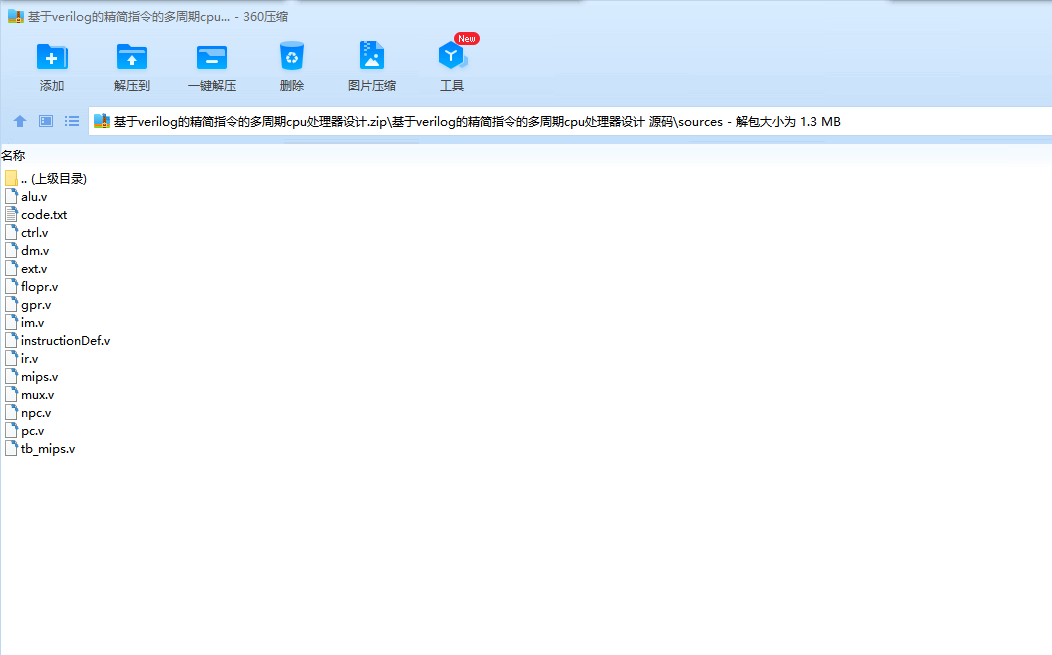

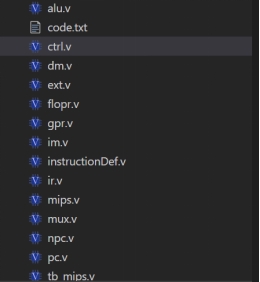

目录结构如图所示:

其中mips.v为顶层结构,tb_mips.v为测试文件,code.txt为IM中要读入的内容。

2.模块定义

2.1 alu

(1)基本描述

alu是该多周期处理器的运算逻辑单元,主要功能是完成需要处理的运算,并将运算结果传输给需要的部件。