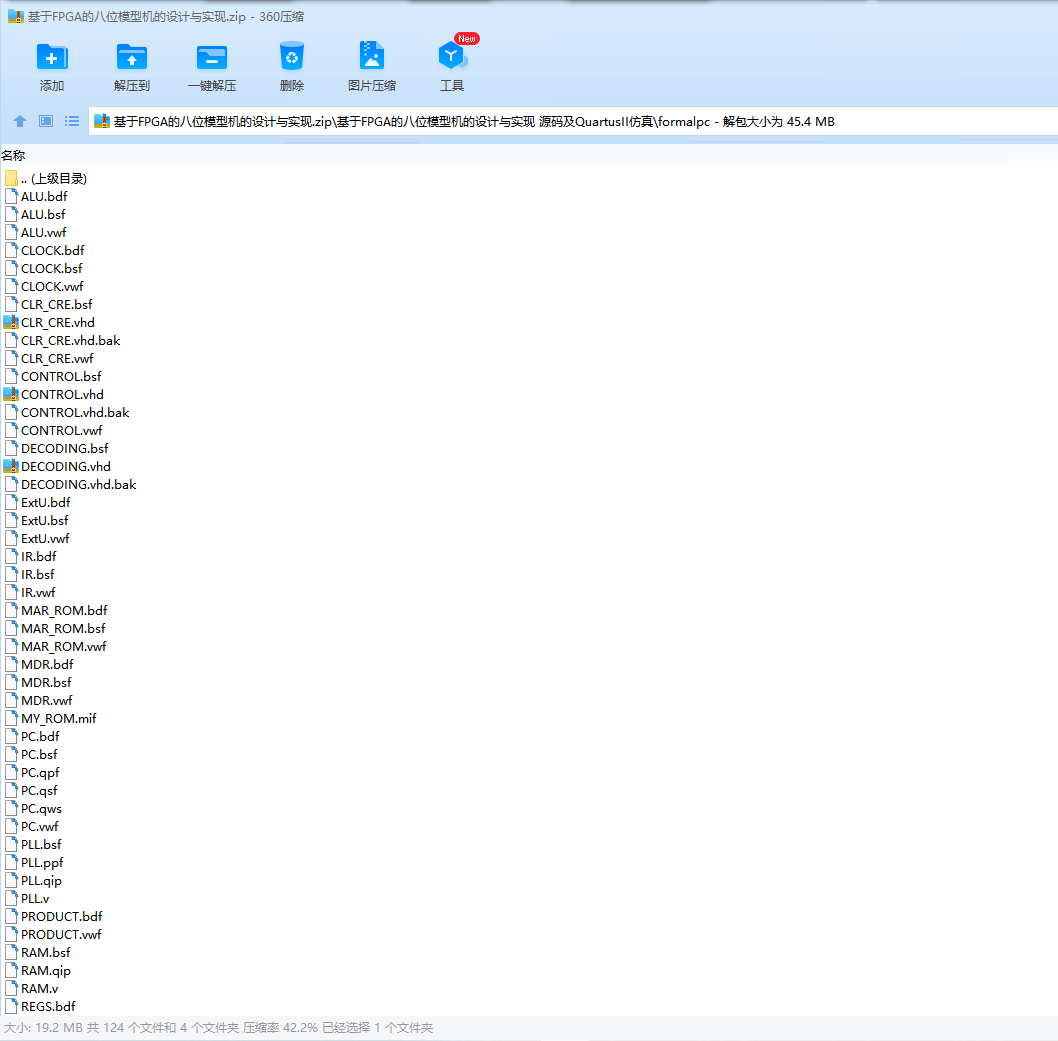

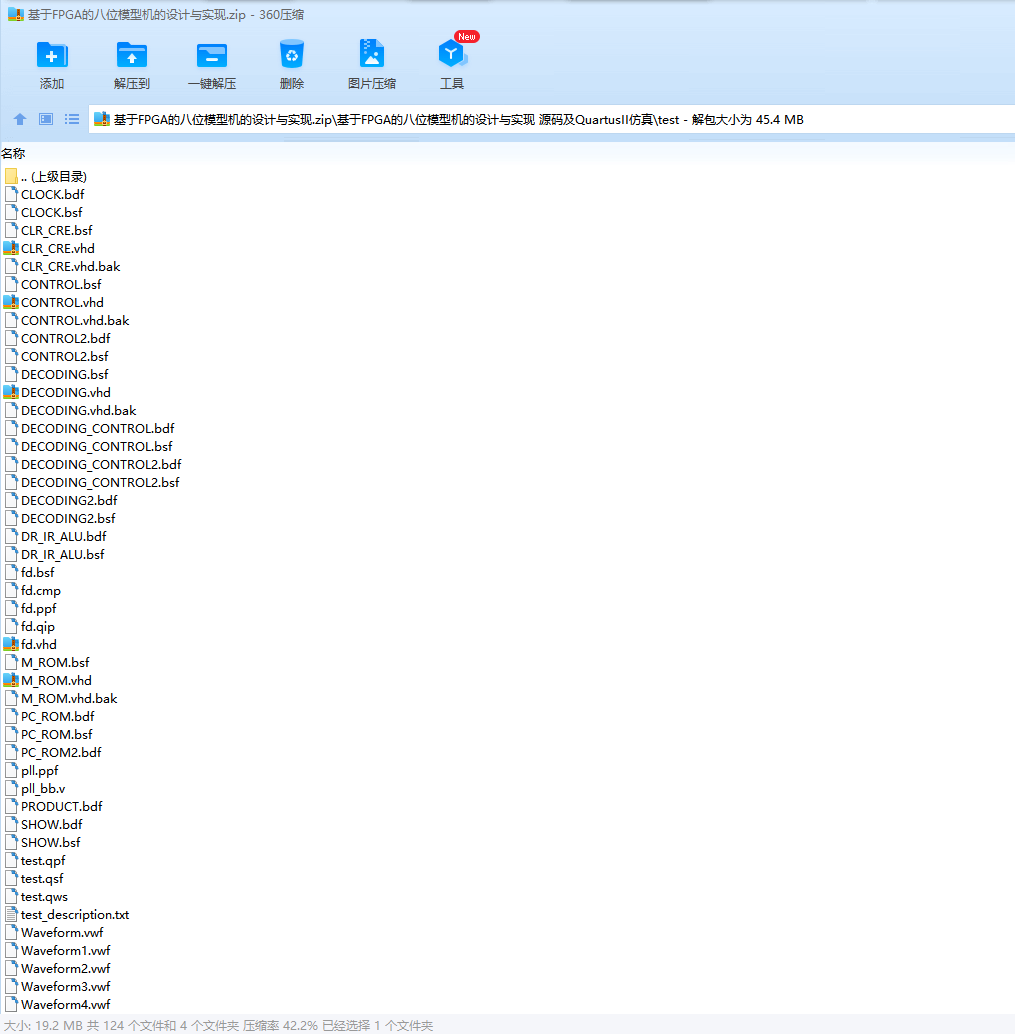

基于FPGA的八位模型机的设计与实现 课程论文+任务书+设计思路+源码及QuartusII仿真

摘要

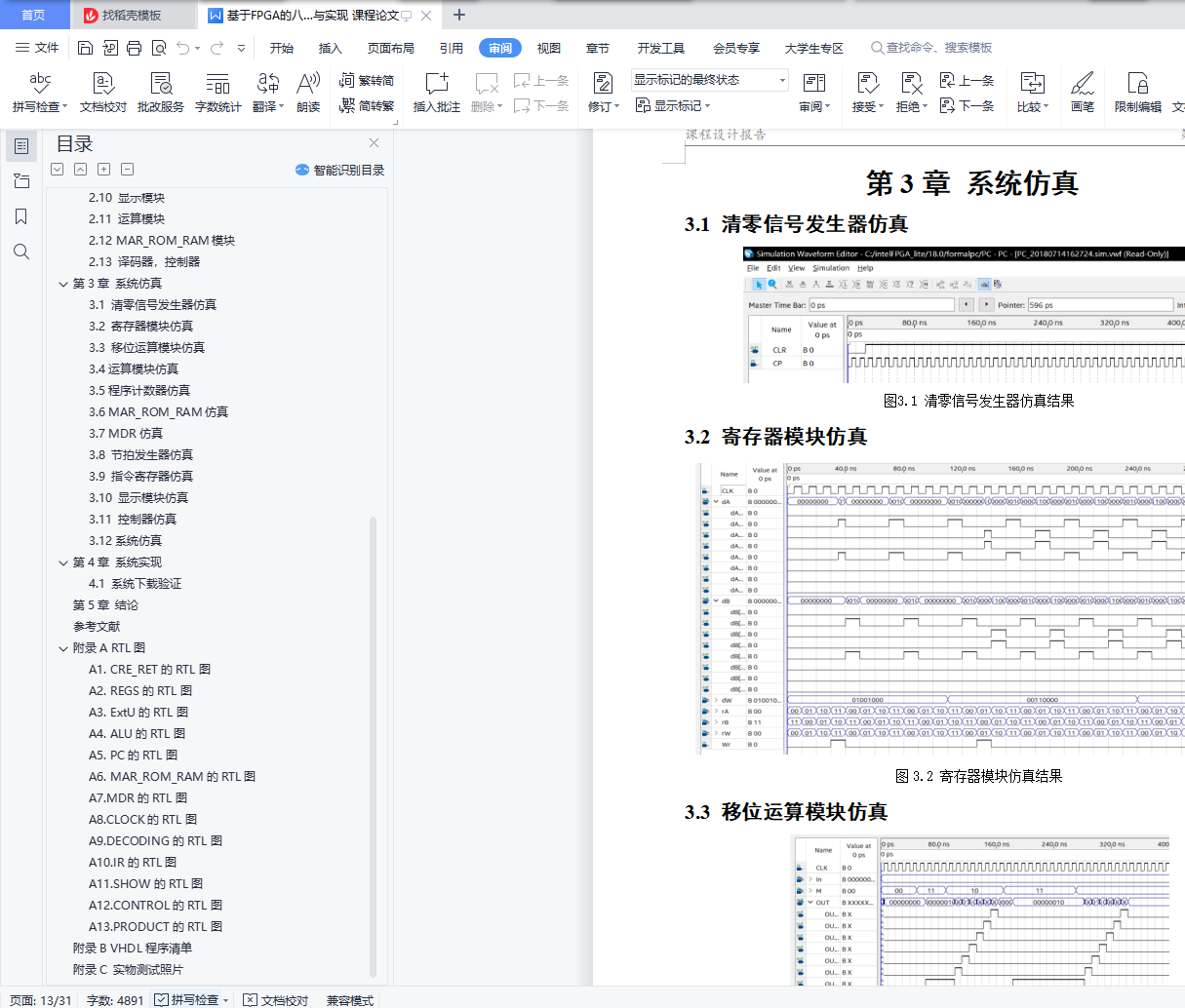

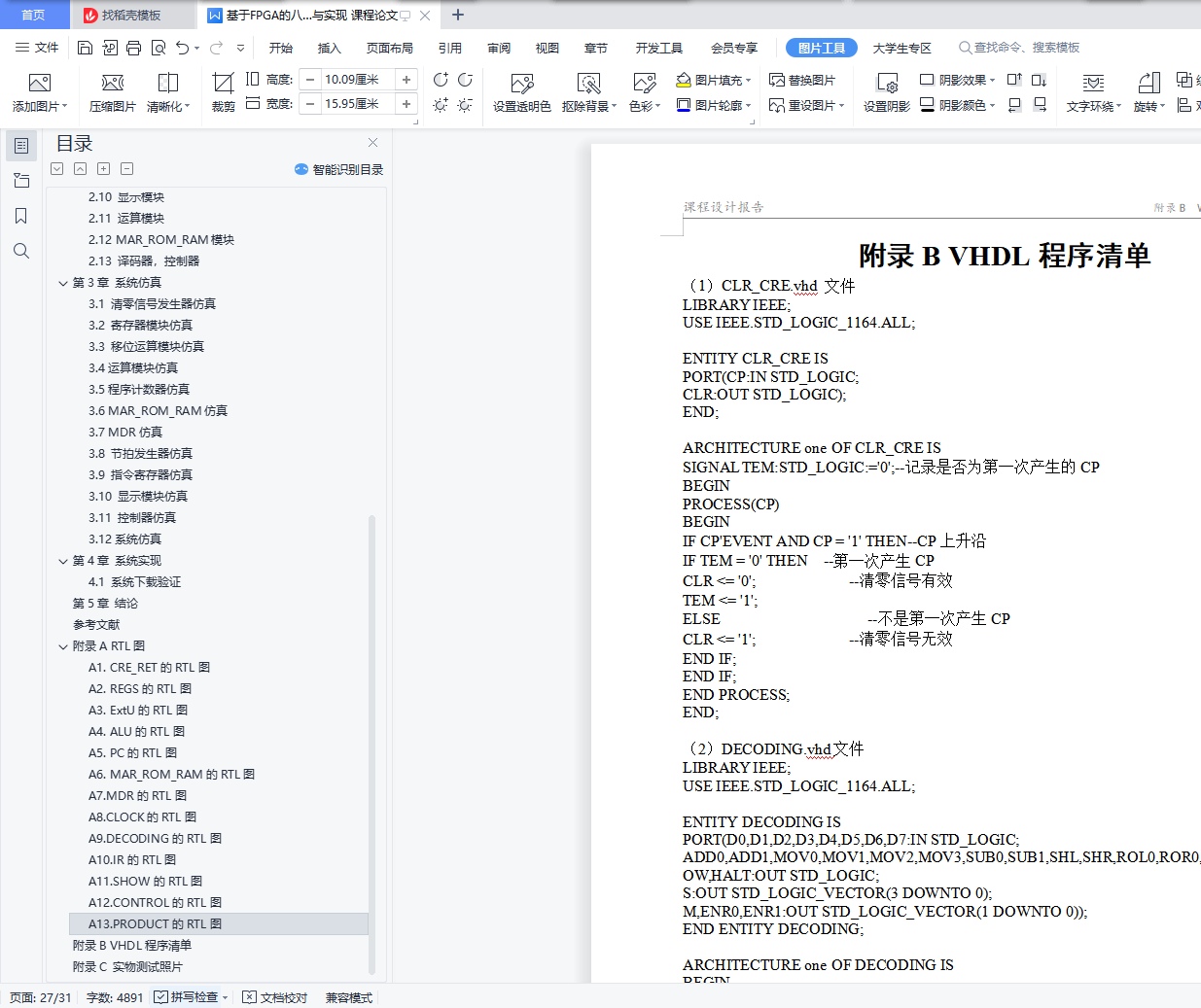

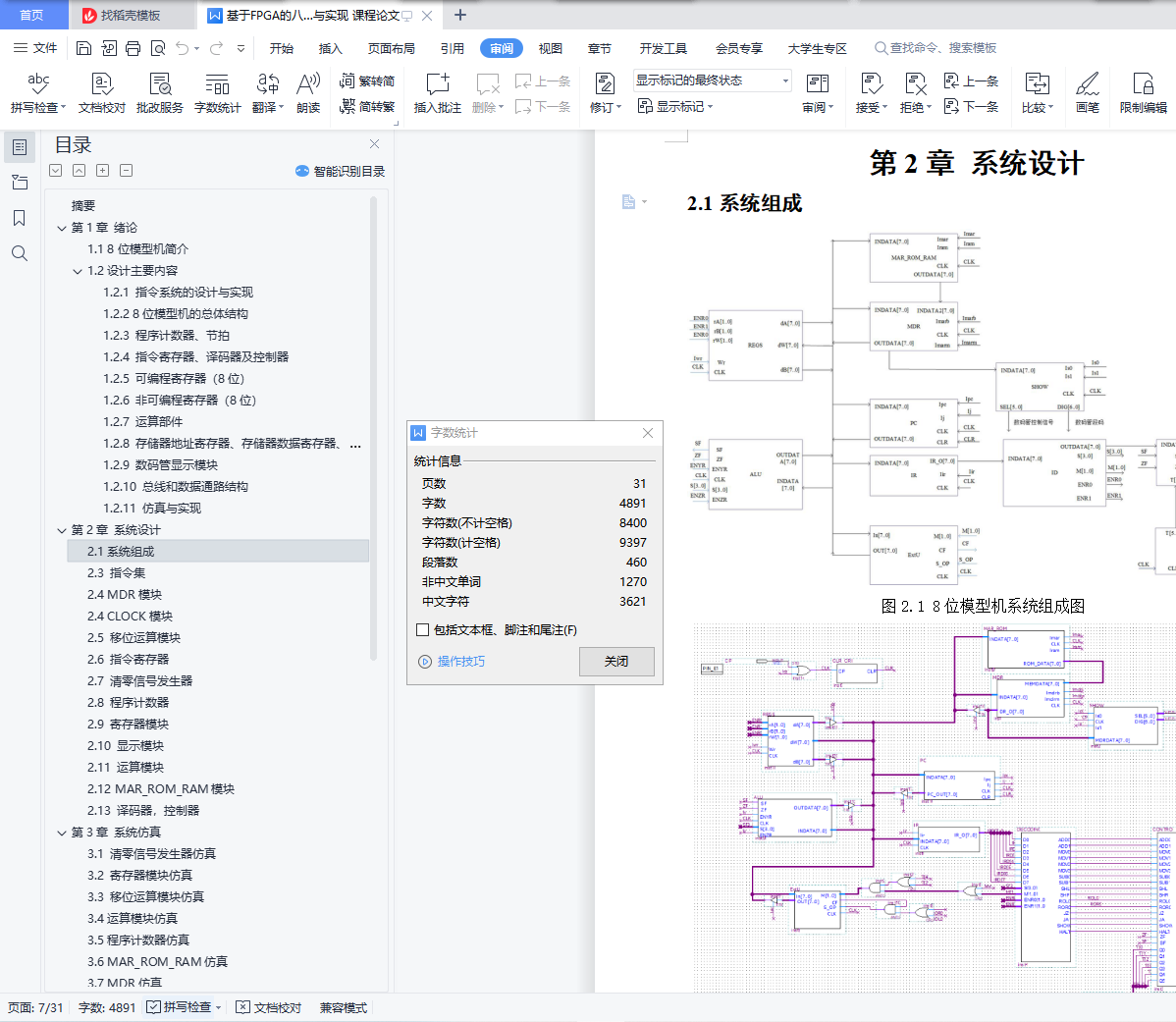

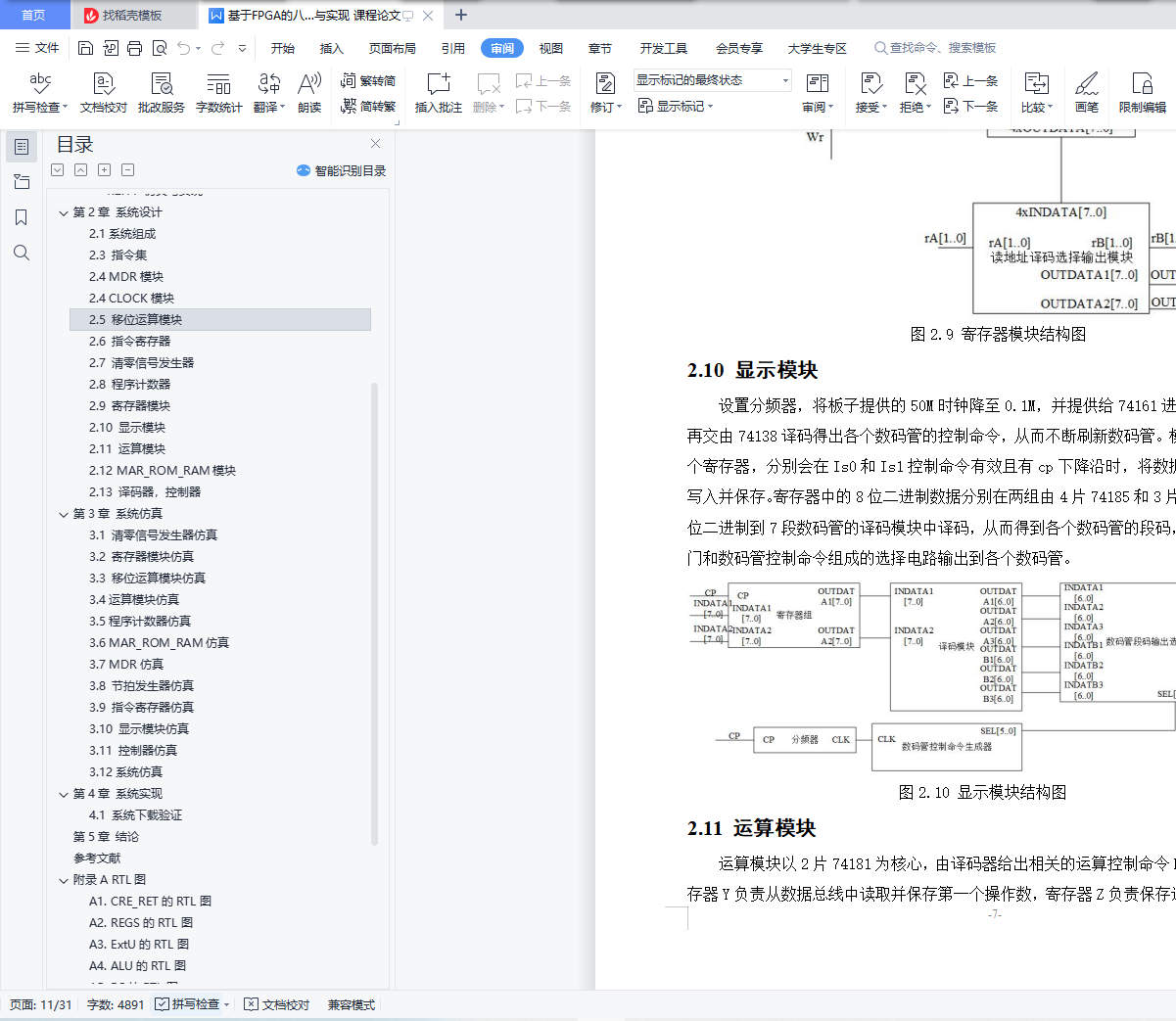

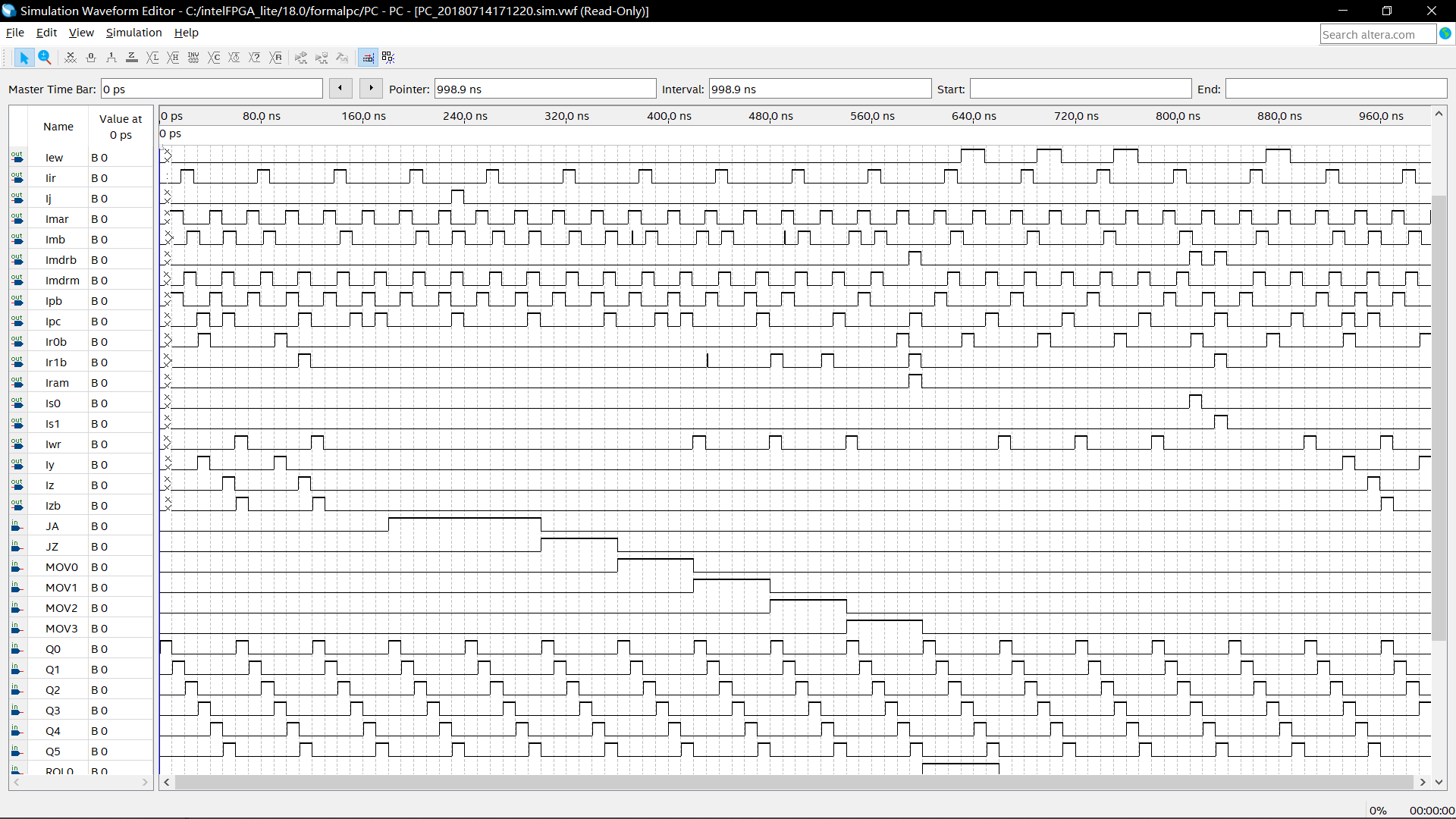

为了更好的学习和理解CPU的基本结构和原理,建立整机的概念,设计了这台8位模型机,并能够下载到FPGA实现。8位模型机整体采取简单的组成模式,每一时钟周期完成最基础的命令操作。模型机包括译码器,ALU,存储器等模块。选用2片74181串行进位方式形成运算器,运用硬布线的方式形成控制信号,实现特定的指令功能。时钟・信号由板子提供上的50MHz的脉冲信号,共有6个节拍。

关键词:FPGA, 8位模型机, 时钟, 节拍。

1.2.8 存储器地址寄存器、存储器数据寄存器、ROM、RAM