基于Verilog的32位单周期CPU处理器的完善设计 论文+程序

目录

Project1

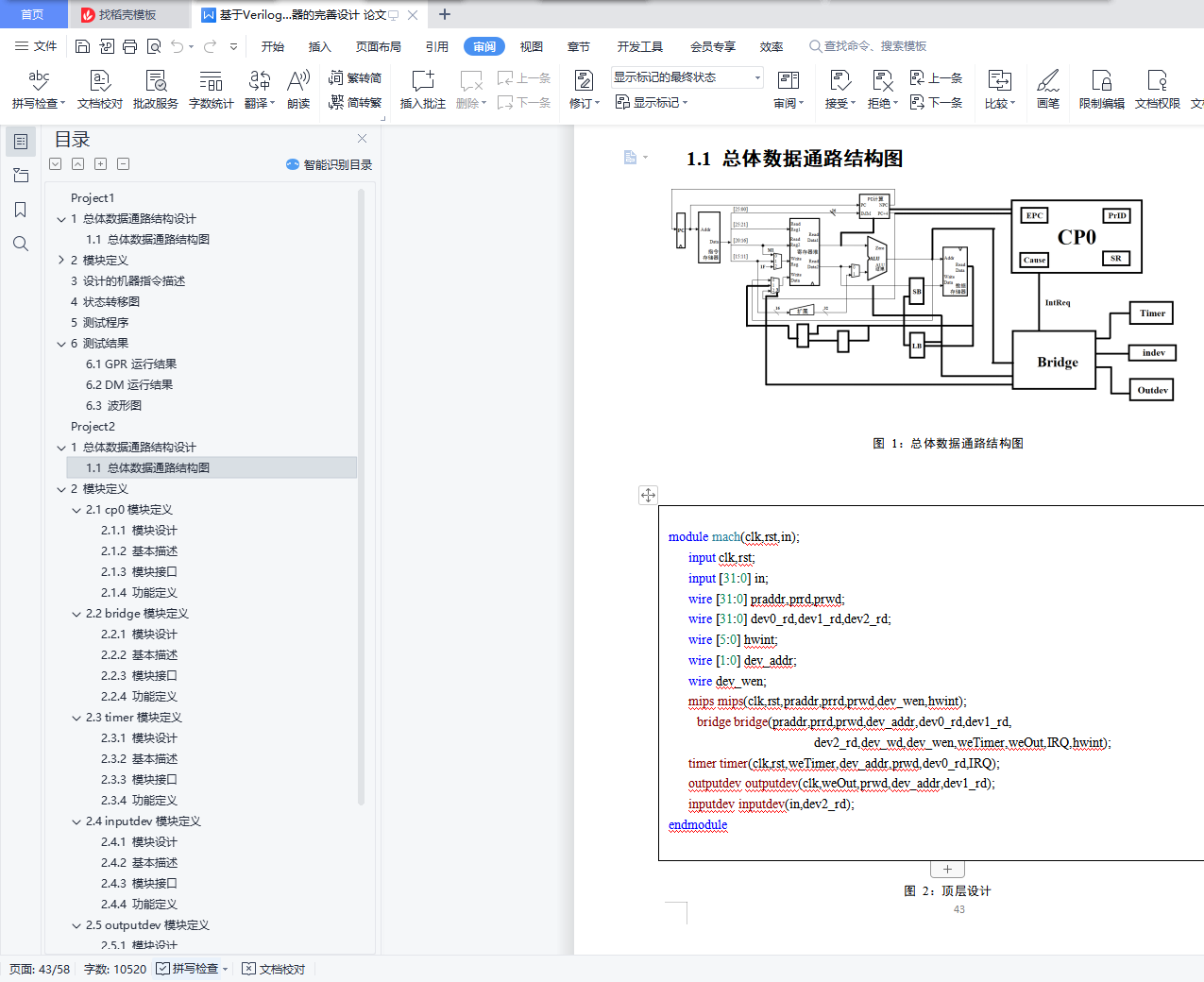

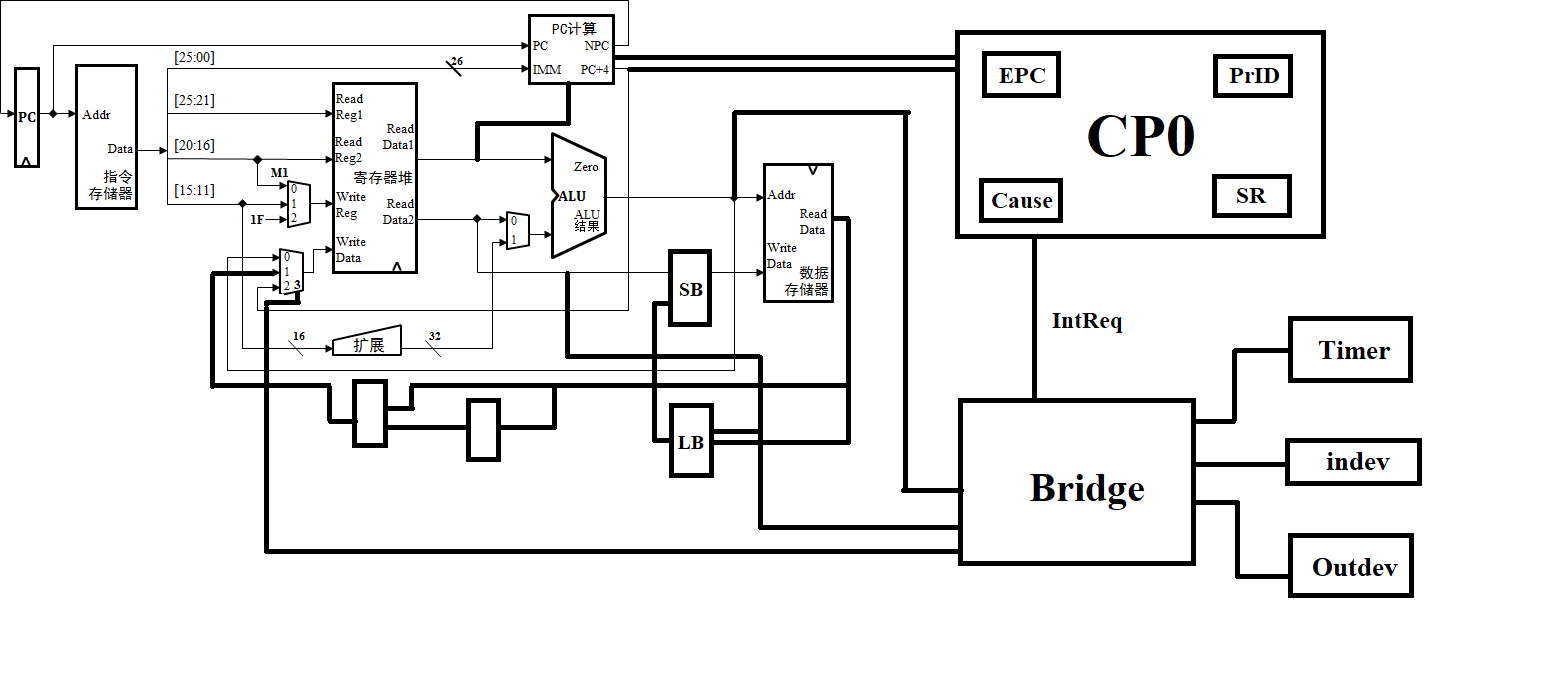

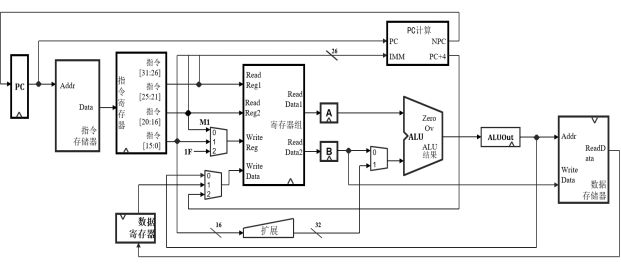

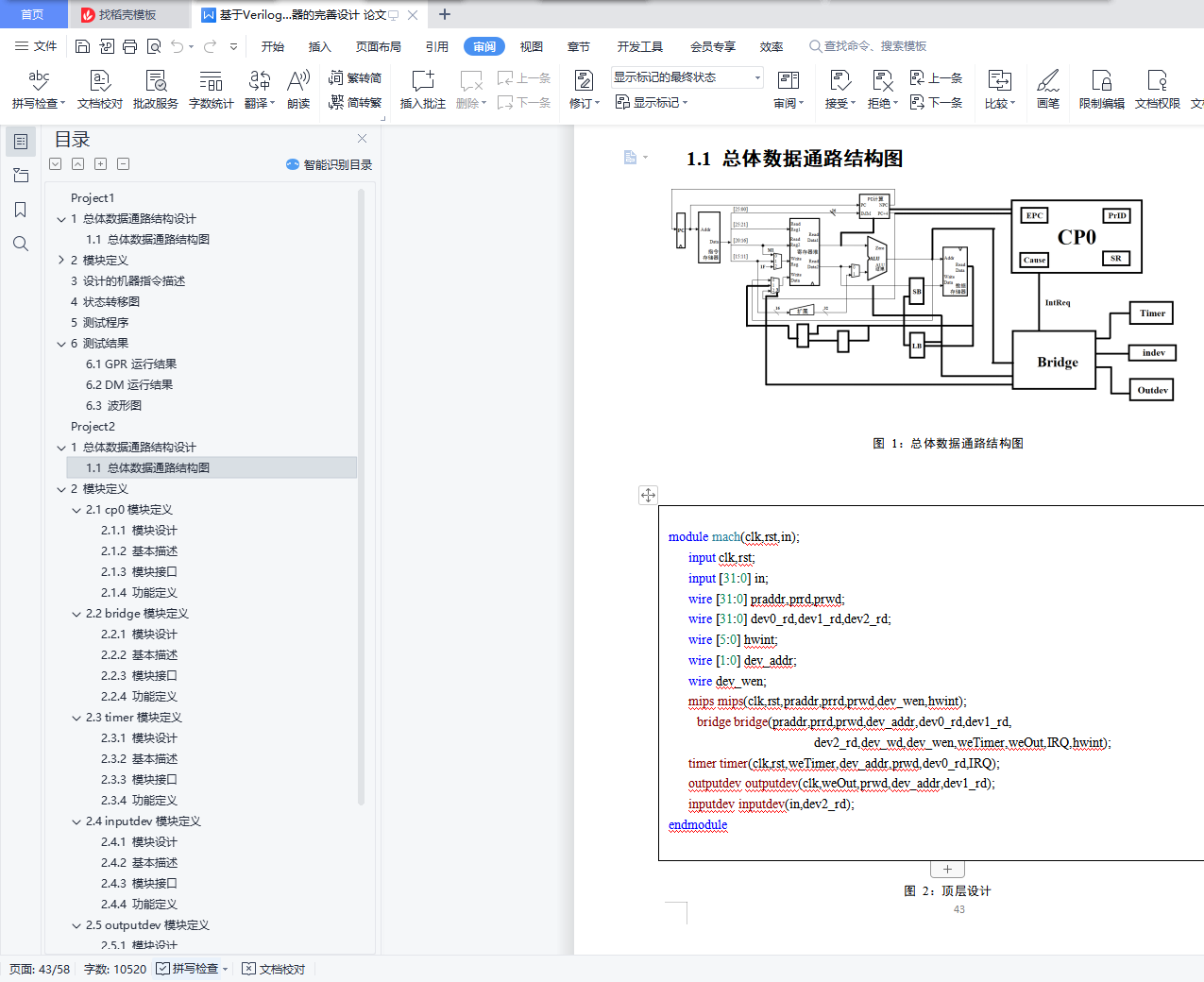

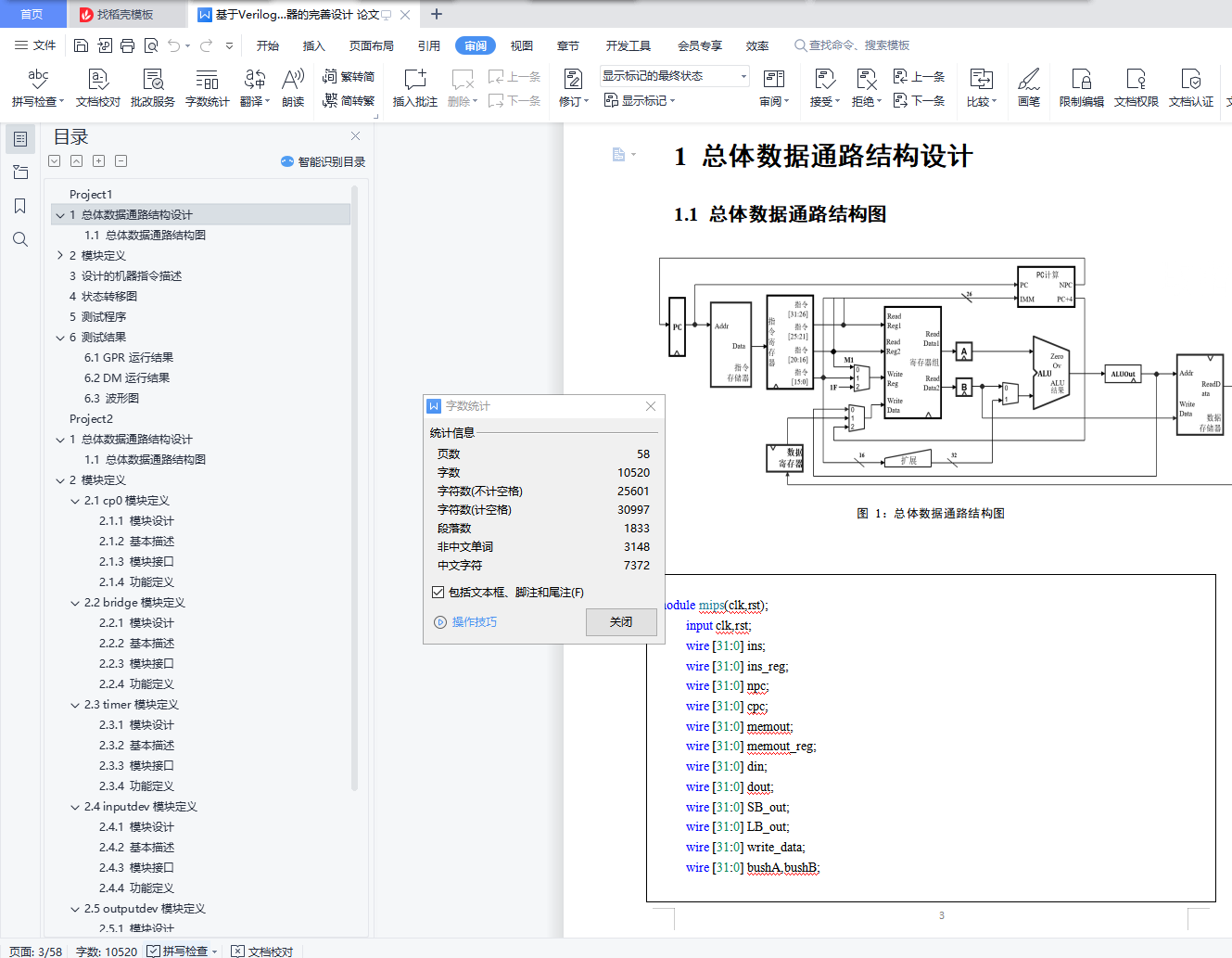

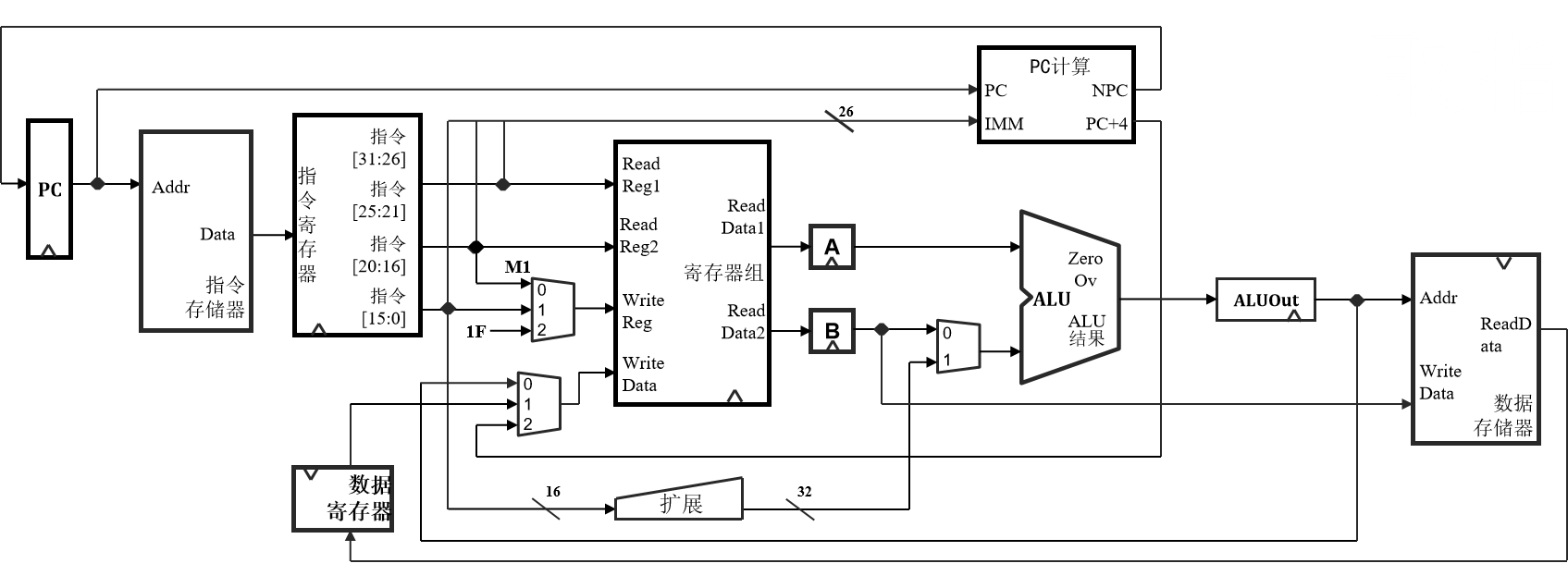

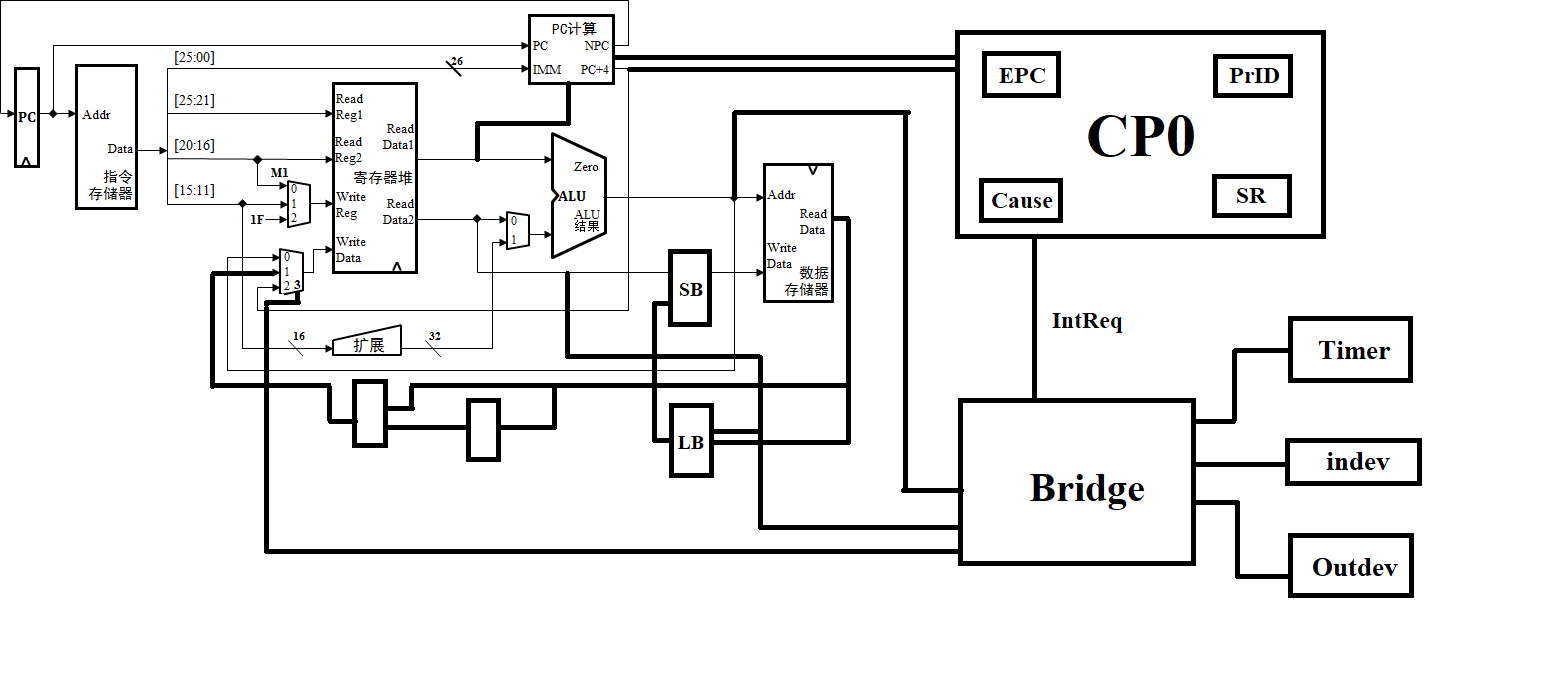

1 总体数据通路结构设计

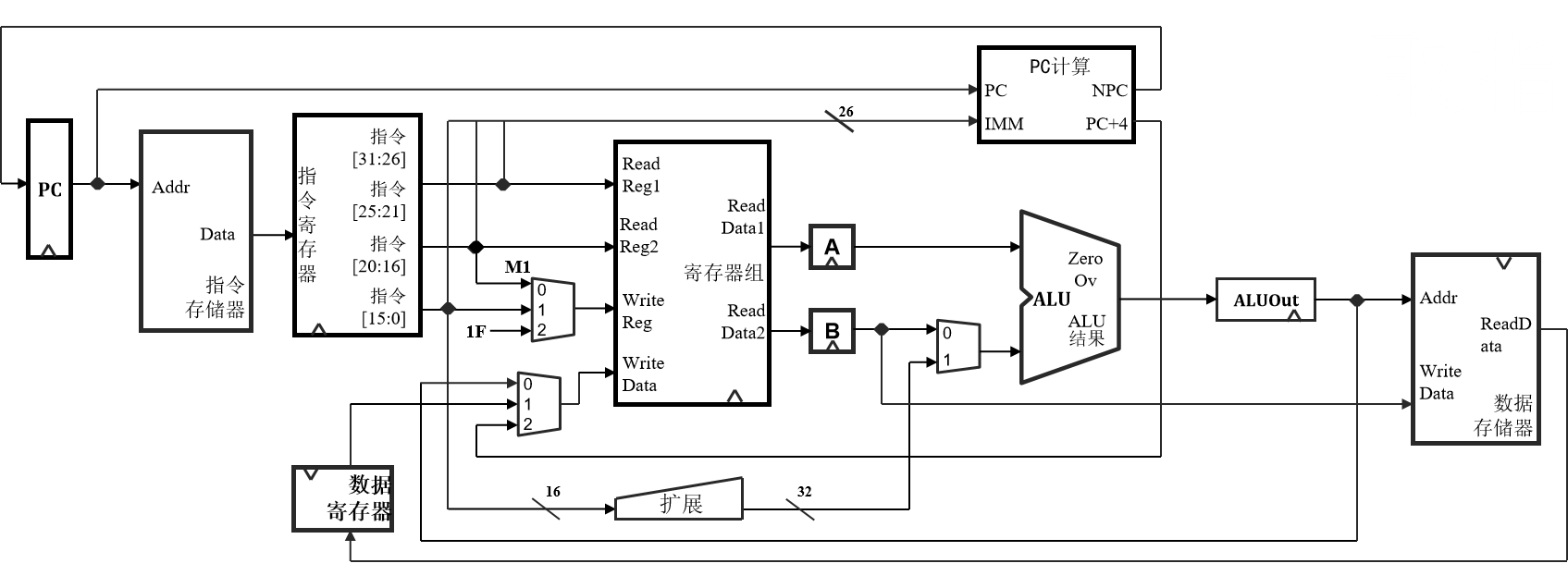

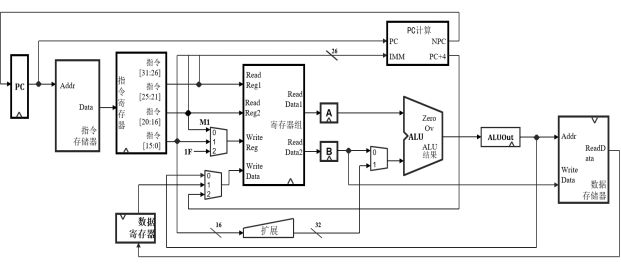

1.1 总体数据通路结构图

图 1:总体数据通路结构图

目录

Project1

1 总体数据通路结构设计

1.1 总体数据通路结构图

图 1:总体数据通路结构图