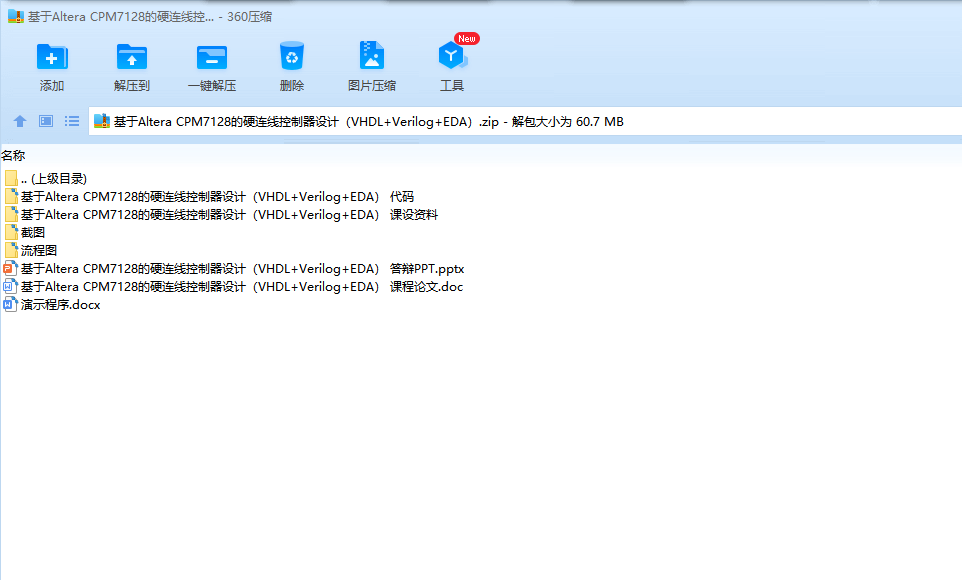

基于Altera CPM7128的硬连线控制器设计(VHDL+Verilog+EDA) 课程论文+课程资料源码+演示程序+答辩PPT

目录

一、 实验目的

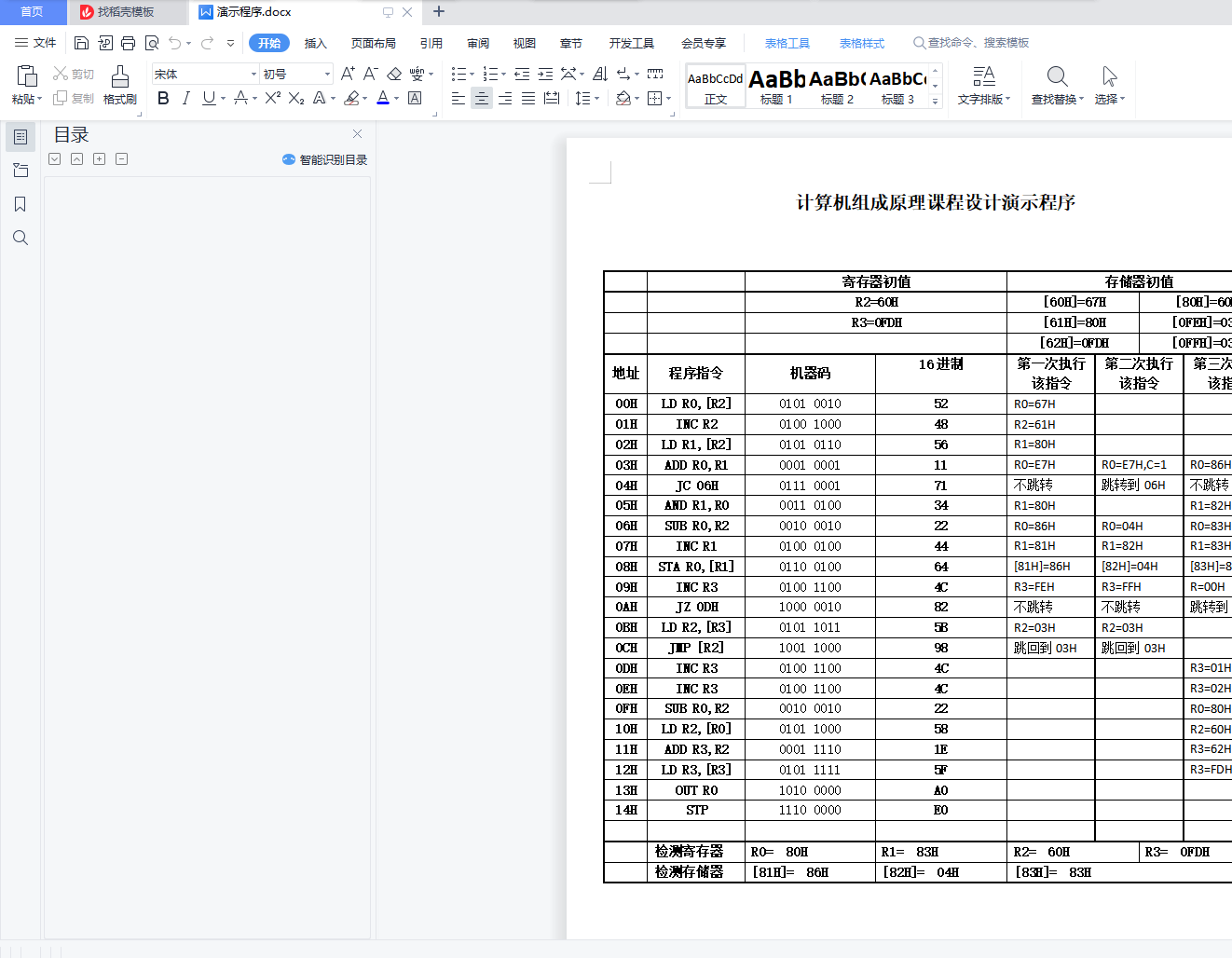

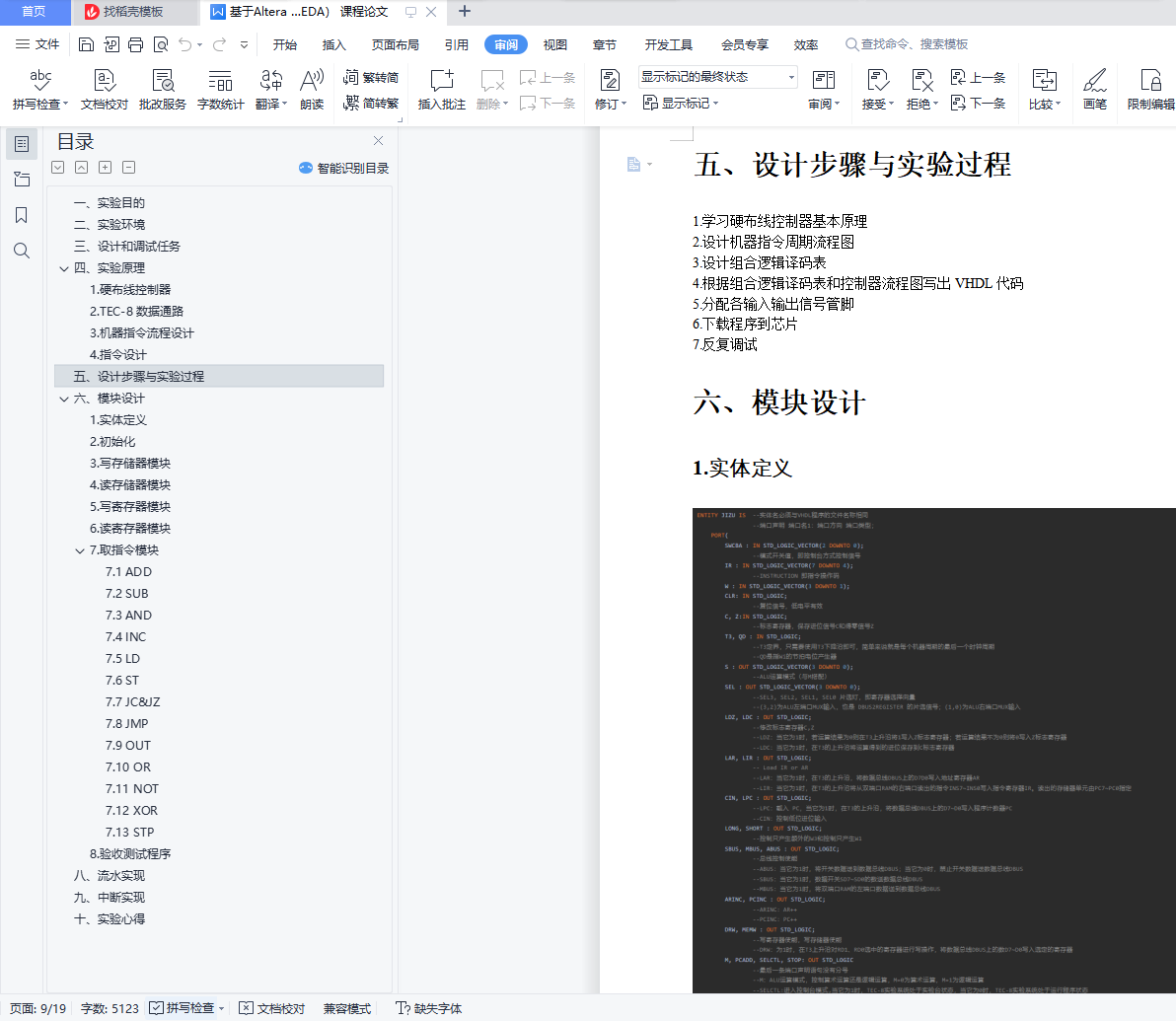

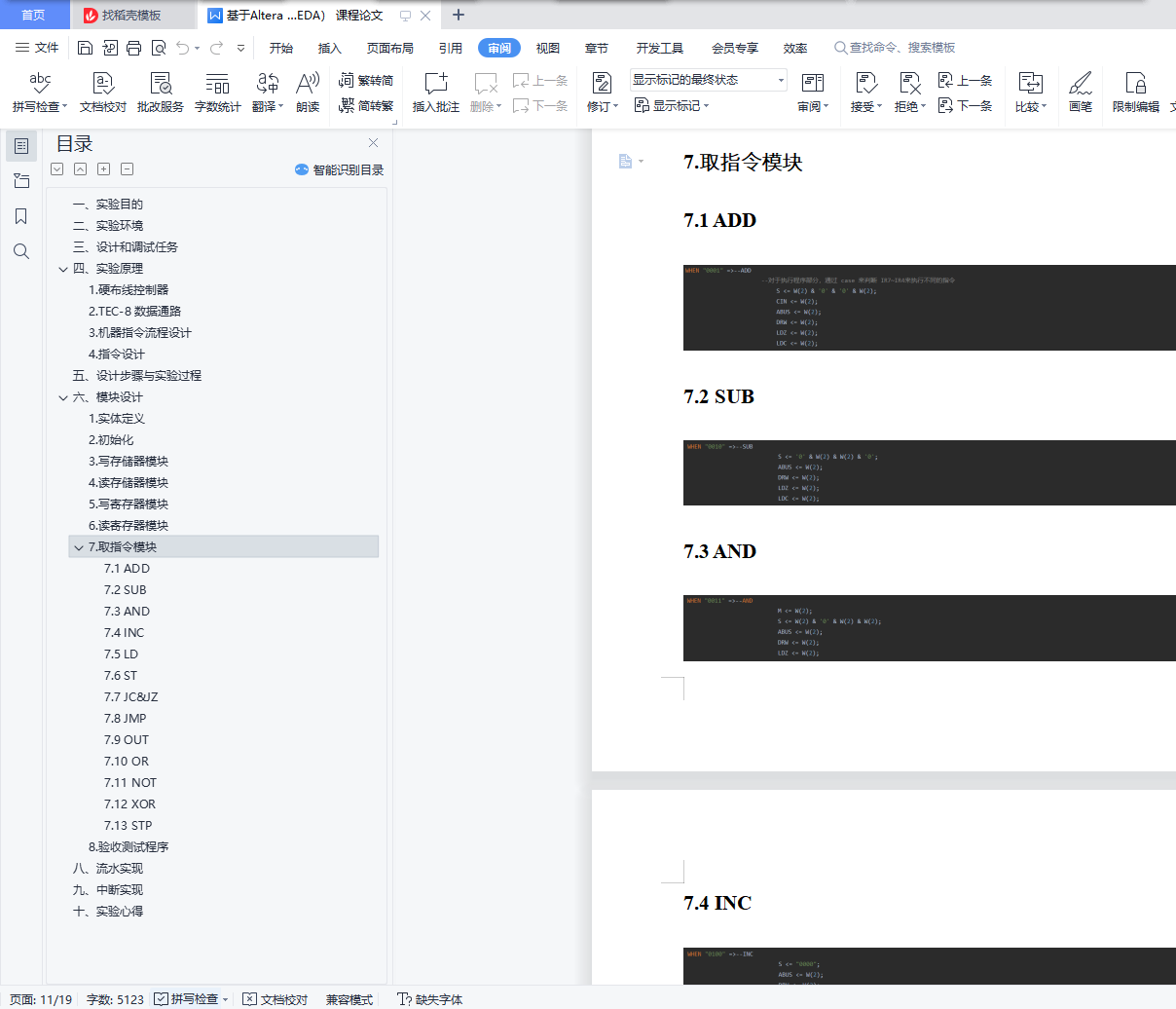

(1)融会贯通计算机组成原理各章节教学内容,通过知识的综合应用,加深对CPU各模块工作原理及相互联系的认识,建立清晰的整机概念。

(2)掌握硬布线控制器的设计方法。

(3)学习运用可编程逻辑技术进行逻辑设计和调试的基本步骤和方法。

(4)培养科学研究的独立工作能力,获得工程设计与组装调试的实践经验。

二、实验环境

开发环境:

• PC微机:EDA设计软件,自行完成逻辑设计、编写程序、编译和下载,调试、运行成功

• TEC-8实验箱

调试工具:逻辑笔万用表数字示波器

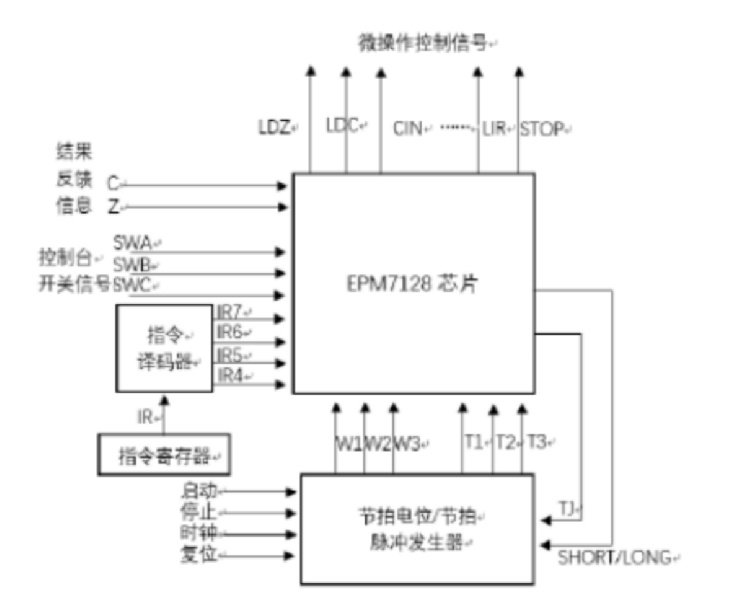

元器件:Altera MAX7000系列CPLD芯片:EPM7128

描述语言:VHDL语言、Verilog语言